2SD864(k) プッシュプル フローティング OPT アンプ

=「直接合成バランスド・シングル」の試作実験

2013/01 宇多 弘

1 いきさつ

1.1 あらまし

今回は "プッシュプル フローティング OPT (出力トランス) アンプ" を試作しました。 なお名称が長いので以下 "PP-FOPT" とします。

この回路方式は 2000年に氏家氏から発案・発表された変形プッシュプル (PP) 回路です。 ネットワーク検索すると、真空管終段による試作例が数例があり、半導体例は見当たりませんでした。 筆者にとっては初体験の回路ですが、半導体でやるか・・・と前川氏の試作例を参考にさせていただき着手しました。

とにかく直接マトモなものに挑戦する自信がなく、まずは小型素子と簡易回路にて失敗経験するぞ、とプロトタイプ試作です。 終段素子は今回もパワー Tr 2SD864(k) ・・・ダーリントン構成にてドライブが容易かつ単段で終段が可、ほぼ無調整で PP が可能なほど揃っていて、プロトタイプ試作向きです。 以前に試作の別項 OPT 併用シングル/PP アンプ、SEPP/シングル切り替え OTL アンプにて使用して様子が判っているつもりでしたが・・・。

1.2 プッシュプル フローティング OPT 回路

PP-FOPT 回路は、通常の PP 回路での正相と逆相の出力素子のたとえば陽極など・・・プレート/コレクタ/ドレイン・・・の間に負荷として(直接ヴォイスコイルまたは)マッチングトランスを接続するものです。 したがって出力信号を電源回路と隔離するため、チョークコイルまたは定電流回路を経由して直接プレート/コレクタ/ドレインに動作電源を供給します。 下記の回路図をご覧下さい。

PP-FOPT 回路は、標準のプッシュプル回路・・・ダブル・エンド PP 回路 =DEPP とは基本的に動作が異なります。

DEPP では上側のエレメントおよび下側のエレメントの各出力は OPT の二つの独立のコイルを通過した各出力が磁界を構成して、磁界レベルにて合成されて二次側のコイルにて回収される訳です。 一方 PP-FOPT 回路では負荷を共用した状態で合成されており、マッチングトランスを併用する場合はインピーダンス変換のみを行うことになります。

1.3 ダブル OPT 回路との区別など

類似の回路としては三浦氏が考案された「ダブル OPT 回路方式」があります。 通常のプッシュプル回路に二個の PP 用 OPT を並列接続して、一つは直流電源の供給に、もう一つは出力信号処理およびインピーダンス変換に・・・電源供給と信号処理の分業のようです。 信号処理 OPT のセンタータップを (C経由) 接地して本来の「ダブル OPT 回路」となります。

信号処理 OPT にマッチングトランス(またはシングル用 OPT)を使用すれば一見 PP-FOPT みたいですが、不完全です。 氏家氏によれば「電源供給 OPT での信号の磁気合成が残り、PP-FOPT 動作として完全ではない。」ということでした。 すなわち独立のチョークコイル経由または定電流回路経由の動作電源供給にて完全な PP-FOPT 動作となると考えられます。 そして DEPP の変型とは「退化回路」か「進化回路」なのか・・・

余談です。 名付け親は不明ですが「パラレル・フィード」という類似の回路名称があります。 クローフ結合を広く解釈して電源供給と信号処理を分業する場合の総称として、シングル構成にも適用でき、終段回路の他にドライバー段にも適用できそうです。 「パラレル」の意味が信号処理と電源供給との「分業」を意図し分離するとの意味ならば、PP-FOPT 回路もこれに該当します。

1.4 直接合成バランスド・シングル、BTL の半分?

筆者は PP-FOPT の回路図を眺めて「直接合成バランスド・シングル」らしいと気がつきました。

バランスド・シングル回路とは、約 10 年ほど前に柳沢氏ほか各氏から試作例が発表されていたと記憶しています。 それは同一構成の OPT 付き真空管式シングル・アンプ二台の一方には正相を他方には逆相を入力し、各々の OPT 二次側を直列接続して出力信号を合成するA級 PP の一種・・・厳密には「二次合成バランスド・シングル」でした。 その頃、筆者達は超三結シングル・アンプを多種試作し、Tr 用小型トランスにて一方に反転入力してモノラルのバランスド・シングル回路として追試験した記憶があります。

以前に筆者が試作した SEPP/シングル切り替え OTL アンプでは、スイッチにて SEPP の下半分の素子に信号入力せず、単に能動体抵抗としてクローフ結合すればシングル OTL アンプになると発想した「SEPP 半休み」回路でした。 もし上半分を「半休み」させれば出力位相反転の同一動作です。 この段階にて PP-FOPT の「半分回路」は試作済みだった訳ですが、 PP-FOPT に手が出る状態ではありませんでした。

そして PP-FOPT 構成では「半休み」シングル OTL アンプ二組みの一方に正相入力、他方には逆相入力してプレート/コレクタ/ドレイン間に負荷を挿入しています。 これはどこかで見たことがある回路だな・・・何のことはない BTL 回路 (=Bridged Trans Less 回路) の上半分を定電流給電に取り替え、負荷にはマッチング・トランスを併用した「BTL 上半休みトランス付き」すなわち BTL を退化させた回路ですね。 従って下半分を「半休み」させても動作は同じ、ただし出力位相は反転です。

そして、むしろ PP-FOPT は "直接合成バランスド・シングル" と命名・呼称するのが適切だろうと考えるに至りました。 英語なら Directly Superimposed Balanced Single amp. =DSBS amp. との呼称になりそうですが・・・。

2 回路構成

2.1 初段と終段

以前に筆者が試作した、シングル兼用 OTL アンプのドライバ段をソックリ再利用しました。 二次側二巻き線入力トランスの代用にて PP 終段入力には SANSUI トランス/橋本電気(株) 製 ST-75 を逆に二個使って一方は位相反転を兼ねてのドライブです。

このトランスは本来 10kΩ/600ΩCT の出力段ドライブ用ですが、逆に使って 1:4 強の電圧ステップアップができます。 なお Tr の固定バイアス用ブリーダ抵抗はドライブ・トランスのターミネータとしては大きすぎながら幾分かの効果がありましょう。 終段を早期に動作確認したいための安易で確実な位相反転兼用の入力トランス・ドライブ、いずれ組み直します。

この状態では通常のバイポーラ Tr または MOSFET に信号入力するはドライブパワー不足または振幅不足ですが、終段がダーリントン構成の 2SD864(k) では何とか利用可能です。 終段が通常の素子ならば正式のドライバー回路以外に小信号用 Tr にてダーリントン回路とするか、または電圧増幅三極管にてダーリントン構成する田中安彦氏考案の「球リントン」回路にて構成できます。

2.2 マッチング・トランス

本アンプの最大の試験対象・・・・コレクタ〜コレクタ間を一次側で結ぶマッチング・トランスには、東栄変成器(株)の T850-600 を採用しました。 一次側は 600/300/0Ω、二次側は 8/4/0Ω、サイズ的に 100V50mA (5VA) のトランスと同一、直流重畳がなければハンドリング・パワーは約 5W と考えました。

PP-FOPT の終段動作では、上下の出力素子が各々逆相の信号を出力し、それが「シーソー」動作にて直接合成されます。 (低インピーダンスが得られれば OTL が可能です。) トランスは信号のみを扱う前提であり、終段出力端の電圧を一致させて直流は流さず、出力信号のヴォイス・コイルとのインピーダンス・マッチ専用となります。 (実際には数 mA 程度までは歪みを感知しませんでしたが・・・)

一方、標準の DEPP では上下の出力管からの PP 用 OPT の二つの一次巻線を通った信号がそれぞれ信号磁界を発生させ、磁気回路にて信号を合成する構造と動作であるから PP-FOPT では全く異なる動作なのです。

2.3 定電流回路の選択

定電流回路を用意するとなれば手軽なのがチョークコイルですが、重量もコストもなかなかのものです。

そこで半導体による定電流回路にしようと発想し、定電圧制御用の LM317T による定電流回路が手軽で良いのですが、「カナクギ」にて手持ちの MOSFET 2SK851 による定電流回路を組んでみました。 BJT/FET の定電流特性を利用するため、一定のベース/ゲート電圧の下での定電流特性を活用する一般的な用法のつもりです。 この MOSFET はアンプ終段などの試作経験がなく手持ち資料も不完全、ともかくソース〜ゲート間およびゲート〜ドレーン間とのブリーダにて電圧設定して定電流動作させ様子を見ることにしました。

3 電源、ヒートシンク、動作点調整

3.1 電源、配置、動作点設定

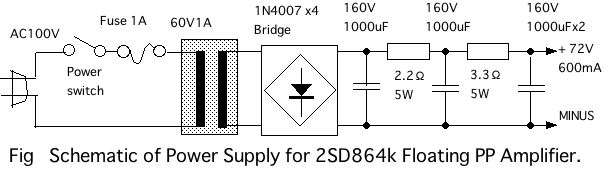

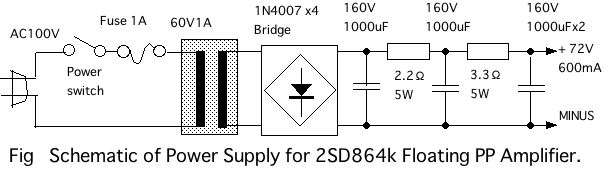

30V1Ax2 両波整流トランスの 60V を 1N4007x4 にてブリッジ整流しました。 シャーシは本文トップの写真に示す木板 300x300/T=18(mm) ブレッドボードとしました。 出力確保のため、パワー Tr の動作点が概ね 60V150mA x2 となるよう、電流帰還型バイアス回路による電圧配分を調整して設定しました。

そして調整後に動作電流を点検すると・・・やはりバラ付きが若干、5% 程度に収まるよう組み合わせを変更したりエレメント交換したり・・・この点は C にて DC カットした SEPP より厳しい訳ですが、事前に選別せずにカンベンしてもらえる限界だなと感じたことです。

3.2 ヒートシンクと冷却ファン

パワーアンプ部分のヒートシンクは 160x50x50(mm) サイズのヒートシンク一個に、パワー Tr 四個を取り付けました。 発熱は約 60V0.6A=36W、寒い日にはナマ温い程度だけど真夏に自然空冷では不足とみて 60x60(mm)〜12V0.09A ファンおよび 9V DC アダプタを追加、ヒートシンク上から吸い上げ強制空冷としました。

定電流回路部分のヒートシンクは様子が判らないので 110x35x40(mm) 二個と大きめにしたのですが、MOSFET 四個の消費電力が 7V x600mA =4.2W と少なく大き過ぎでした。 ホノカに暖まるだけなので、適宜サイズのアルミ板または金属シャーシなら直接取り付けで良さそうです。

3.3 試運転してみると・・・

一発目をつぶってパワー on して様子を見ると、とにかく定電流回路のブリーダ抵抗が熱せられて MOSFET は冷たいまま S-D 間電圧がかなり高い状態です。 それでもアンプ部分には若干の電圧が掛かっているので、もしかして・・・とスピーカを繋ぎ信号入力したら歪んだ小音量の出力があります。

「アリャ定電流回路は失敗か」・・・考えてみたらソース〜ゲート間の電圧設定が低すぎて MOSFET は眠ったままだったのですね。 そしてブリーダ抵抗が定電流素子の代用となり、電圧不足ながら取りあえずアンプ部分は動作した訳です。 期せずしての「抵抗による定電流回路代用」の動作確認には苦笑です。

「これじゃ話にならん」とソース〜ゲート間の抵抗値を上げて・・・ゲート電圧を上げてゲート〜ドレーンの電圧が「ポン」と低くなったところで、 MOSFET の平坦特性に入ります。 さらにゲート電圧を若干上昇させました。

とにかく PP-FOPT 回路の動作確認を急ぎ、時定数関係はテキトーながらなんとか所要帯域を保ちました。 終段 Tr の動作点を予定値近くに設定して、微調整にかかりました。 MOSFET が変な発振を起こすので適当なCをゲート〜ドレーン間に並列接続しましたが、大きすぎで高域に影響しているでしょう、いずれ減らして様子を見ます。

これでチョークコイルへの逃避は回避しました。 下記のようにチョーク、抵抗、定電流の三者を比較すると、定電流回路が有利らしいです。

チョーク :抵抗ロスが少し、 重い、帯域やや心配、高価 。

抵抗器 :抵抗ロス大・発熱大、軽い、帯域万全、 まず安価 。

定電流回路:抵抗ロスが少し、やや軽い、帯域やや心配、やや安価 。

3.4 バランス調整

本アンプに使用のパワー Tr はバラ付きが少なく、固定バイアス用のブリーダによるベース電圧設定にて数%程度に収まり、PP の上下バランスは若干電流の多い側のコレクタ〜ベース間のブリーダ抵抗に可変抵抗を挿入して 600Ωマッチング・トランス一次端子間の微小電圧を監視し、ゼロにするつもりでした。

ところがその前に、定電流回路のバラ付きの調整が必要となりました。 バランス調整以前に供給電圧が食い違ってゼロ調整はオアズケです。

組み付けた一つのパワー Tr ユニットを「基準負荷」として、各定電流回路の出口電圧を当たると MOSFET およびブリーダ抵抗の僅かなバラツキによるものと思われる数%以下のバラツキが検出でき、R/L 各々の定電流回路セットの出口電圧が高い側のゲート〜ドレーン間ブリーダ抵抗に数%程度を挿入し加減して、前記の「基準負荷」にてほぼ一定値に追い込んだ上で、PP の上下バランスは mV オーダに調整しました。

このあたりは性能値がよく揃ったチョーク経由なら不要かもしれません。

3.5 マッチング・トランスの変更試験

試みに 100V/12V2A 仕様のヒーター・トランス (556Ω/8Ω換算) および真空管用 5kΩ/8Ω SG タップ付きシングル OPT のB~SG 間 (1kΩ/8Ω換算) を、初期設定したマッチング・トランスと交換してみました。 トランスが変わってやや発振気味になったのは意外でしたが、終段の B/C に発振止め抵抗を挿入し抑止しました。 いずれもマッチング・トランスを抜く音は得られませんでしたが何とか実用になりそう、調整余地はありそうです。

そして PP-FOPT には発振しやすい要素があるなと感じました。 安定動作のためにはローインピーダンスの終段エレメントとか、負荷のインピーダンス特性の吟味等の、基本的な設計配慮が必要のようです。

3.6 追加の改造

とにかく PP-FOPT 回路の見当がつき、欲が出てきて「もう少し音が良くならんかいな」と改造にかかりました。

定電流回路の時定数が気になり、S-G 間キャパシタを大きくして結構低音の厚みが増し「低音漏れ」がバレました。

動作電圧を下げた方が素直な音になるので、出力低下を我慢してブリッジ整流だった電源回路を両波整流に変更しました。 そして終段の固定バイアス・・・C~B 間のブリーダ抵抗を減少させて、動作電流をある程度確保しました。 なお変更後の電源回路図は省略します。

若干の NFB を掛けるため、初期のトランス位相反転は J-FET 回路に変更できないか検討しました。 位相反転には差動回路例が圧倒的に多いのですが、マイナス電源で引くのが面倒なので強引に P-K 分割相当の「S-D 分割」回路をトライ、円滑に動作しました。 なお終段のゲインが充分あり、入力を直接位相反転してもゲインは若干余っています。 ということはトランス・ドライブではミスマッチしていた可能性が露見した訳で、再検討を要します。

マッチング・トランスの二次側から初段のエミッタに直接 over-all NFB を掛けても安定に動作し、パワー不足ながらまともな音になりました。

4 最後に

今回は諸性能も調整も不完全ながら、初体験の「直接合成バランスド・シングル」半導体アンプが一応の成果を得ました。

PP-FOPT 回路は真空管・半導体をとわず、適宜のマッチング・トランスを確保し、発振し易いので対策を講じて、A 級 PP 回路が容易に構成できる・・・自由度と汎用性の高い回路であると感じました。 今回の試作経験を踏まえて如何に大形化・高性能化するか・・・が次の課題です。

改訂記録

2013/01:初版、解説と試作経過